Journal of Engineering Research and Reports

15(1): 29-33, 2020; Article no.JERR.59194 ISSN: 2582-2926

# Lead Scratch Resolution through Wirebonding Process Optimization on QFN Packages

Jonathan Pulido<sup>1</sup>, Frederick Ray Gomez<sup>1</sup> and Edwin Graycochea Jr.<sup>1\*</sup>

<sup>1</sup>New Product Development and Introduction, STMicroelectronics, Inc., Calamba City, Laguna, 4027, Philippines.

Authors' contributions

This work was carried out in collaboration among all authors. All authors read, reviewed and approved the final manuscript.

#### Article Information

DOI: 10.9734/JERR/2020/v15i117136 <u>Editor(s):</u> (1) Dr. Guang Yih Sheu, Chang-Jung Christian University, Taiwan. (1) Ahmed Mohamed Yahya, University of Nouakchott Al Aasriya, Mauritania. (2) Abioye, Adesoye Idowu, University of Ilorin, Nigeria. Complete Peer review History: <u>http://www.sdiarticle4.com/review-history/59194</u>

**Original Research Article**

Received 10 May 2020 Accepted 16 July 2020 Published 31 July 2020

# ABSTRACT

With the continuous trend of new technologies in semiconductor manufacturing assembly, challenges and issues are unavoidable. This paper presents an improvement done in quad-flat noleads (QFN) leadframe package to resolve the quantity of unit rejection due to leads scratch underneath the leadframe. Moreover, the reject manifestation was captured after wirebonding process. Parameter optimization particularly for the second bond with the combination of bond force and bond scrubbing parameters was done to totally eliminate this type of issue after wirebonding process. With the wirebonding process optimization and improvement done, a reduction of 95 percent of leads scratch occurrence was achieved.

Keywords: QFN; leadframe; wirebonding; bond force; bond scrubbing.

# **1. INTRODUCTION**

One of the greatest trials for semiconductor assembly manufacturing is to maintain its

competitive market position and its value as well. New technologies have a given manufacturability issues encountered during lot processing and one of the particular process mostly affected is

\*Corresponding author: Email: edwin.graycocheajr@st.com;

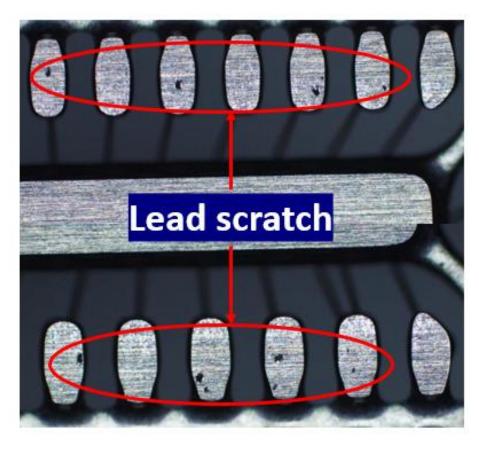

Fig. 1. Lead scratch manifestation

the wirebonding process. Wirebonding process is responsible in attaching the wires to provide electrical connections through combination of heat, pressure and thermosonic energy. This paper presents a solution and improvement done to process this type of assembly reject lead scratch by optimizing the parameter bond force and bond scrubbing. Bond force is the amount of additional pressure applied during the bonding cycle while bond scrubbing is the duration applied through bond forced with heavily pressed on the leads of the leadframe material. To guarantee its integrity during the processing, wirebond process is incorporated with a multiple of criteria such as, ball size, ball height, ball aspect ratio, wire-pull test, ball shear test, stitchpull test, loop height, intermetallic coverage, contact angle, and visual inspection. This wirebond criteria is performed after machine conversion or set-up to ensure the product is reliable when loaded to a reliability test. Fig. 1 above shows the defect manifestation of lead scratch.

#### 2. LITERATURE REVIEW AND PROBLEM IDENTIFICATION

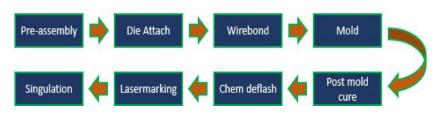

A complete assembly process flow for quad-flat no-leads (QFN) device in attention from preassembly to singulation is illustrated in Fig. 2. Important to note that assembly process flow varies with the product and the technology [1-3]. Furthermore, with new and continuous technology trends and breakthroughs, challenges in assembly manufacturing are inevitable [4-7].

Lead scratch is the top major assembly reject in wirebonding process, and this was seen during the lot processing of the device. This lead scratch is caused by a high bond force and high bond scrubbing during attaching of wires on the leads. One of the most challenging issue in wirebond process is to fine tune the parameter to have a good response in the actual unit and to have a good reliability as well.

Pulido et al.; JERR, 15(1): 29-33, 2020; Article no.JERR.59194

Fig. 2. QFN assembly process flow

# 3. PROCESS SOLUTION AND DISCUSSION OF RESULTS

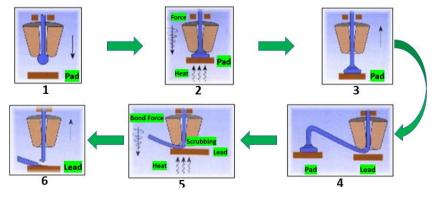

An improved and enhanced process solution in wirebonding is widely done with the combination of bond force and bond scrubbing parameter optimization. Fig. 3 illustrates the wirebonding sequence. The wire used is usually made either of gold or aluminum, with copper wires added recently in semiconductor assembly manufacturing industry [4,8].

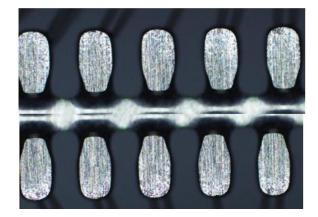

With the combination of bond force and bond scrubbing parameter optimization, no lead scratch occurrence was seen after implementing the improvement in wirebonding process. Fig. 4 shows the actual unit with no lead scratch using

the optimized bond force and bond scrubbing parameter. With this improvement, backside inspection on the leads is not anymore needed, thus saving resources and time. Furthermore, faster delivery of units and business movement could be realized.

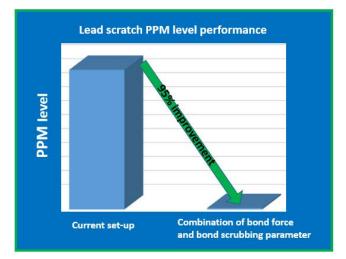

The optimized parameter would eventually have a good reliability test and a good solderability test. This optimized bond parameter would eventually serve as the good stitch formation, shown in Fig. 5, which also passed the destructive wire-pull test. A 95 percent improvement shared in Fig. 6 was achieved for lead scratch. Note that actual parts per million (PPM) level are intentionally not shown due to confidentiality.

Fig. 3. Wirebonding sequence

Fig. 4. Actual unit with no lead scratch using the optimized parameter

Pulido et al.; JERR, 15(1): 29-33, 2020; Article no.JERR.59194

Fig. 5. Actual unit with a good stitch formation

Fig. 6. PPM level performance of lead scratch

## 4. CONCLUSION AND RECOMMENDA-TIONS

Lead scratch mitigation was successfully realized through comprehensive wirebond process characterization and optimization for QFN leadframe package. Parameter optimization particularly for the second bond with the combination of bond force and bond scrubbing parameters were employed, resulting to 95 percent improvement on the leads scratch occurrence reduction.

The wirebond parameter optimization in this study could be used for future works on other QFN products with similar configuration. Comparison of existing works and other studies

should also be included for added analysis. Worth noting is that continuous process improvement is really important to sustain the high quality performance of semiconductor products and their assembly manufacturing. Studies and learnings shared in [4,7-11] are helpful in reinforcing robustness and optimization of assembly processes particular at wirebonding process.

### ACKNOWLEDGEMENT

The are sincerely authors thankful to New the Product Development & Introduction (NPD-I) team and the Management Team (MT) for the continuous support.

#### **COMPETING INTERESTS**

Authors have declared that no competing interests exist.

#### REFERENCES

- 1. Geng H. Semiconductor manufacturing handbook. 2nd ed. McGraw-Hill Education, USA; 2017.

- Doering R, Nishi Y. Handbook of semiconductor manufacturing technology. 2nd ed. CRC Press, USA; 2007.

- 3. Harper C. Electronic packaging and interconnection handbook. 4th ed. McGraw-Hill Education, USA; 2004.

- Tan CE, Liong JY, Dimatira J, Tan J, Kok LW. Challenges of ultimate ultra-fine pitch process with gold wire & copper wire in QFN packages. 36th International Electronics Manufacturing Technology Conference. Malaysia. 2014;1-5.

- Saha S. Emerging business trends in the semiconductor industry. Proceedings of PICMET '13: Technology Management in the IT-Driven Services (PICMET). USA. 2013;2744-2748.

- Sumagpang Jr. A, Rada A. A systematic approach in optimizing critical processes of high density and high complexity new

scalable device in MAT29 risk production using state-of-the-art platforms. Presented at the 22nd ASEMEP Technical Symposium, Philippines; 2012.

- Lay Yeap L. Meeting the assembly challenges in new semiconductor packaging trend. 34th IEEE/CPMT International Electronic Manufacturing Technology Symposium (IEMT). Malaysia. 2010;1-5.

- Lall P, Deshpande S, Nguyen L. Reliability of copper, gold, silver, and pcc wirebonds subjected to harsh environment. IEEE 68th Electronic Components and Technology Conference (ECTC). USA. 2018;724-734.

- Sumagpang Jr. A, Graycochea Jr. E, Gomez FR. Package design improvement for wire shorting resolution. Journal of Engineering Research and Reports. 2020;11(2):41-44.

- 10. Pulido J, Gomez FR, Graycochea Jr. E. Wirebond process improvement with enhanced stand-off bias wire clamp and top plate. Journal of Engineering Research and Reports. 2020;9(3):1-4.

- Moreno A, Graycochea Jr. E, Gomez FR. Specialized wire bond process configuration on advanced multi-die package. Journal of Engineering Research and Reports. 2020;12(4);1-5.

© 2020 Pulido et al.; This is an Open Access article distributed under the terms of the Creative Commons Attribution License (http://creativecommons.org/licenses/by/4.0), which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Peer-review history: The peer review history for this paper can be accessed here: http://www.sdiarticle4.com/review-history/59194